零知识处理单元(ZPU)设计方案介绍—— 多功能及可编程的ZK硬件加速器

TL;DR:

在本博客中,我们提出了零知识处理单元(ZPU),这是一种通用的可编程硬件加速器,旨在解决零知识处理的新需求。

我们将介绍ZPU架构和设计注意事项。我们解释了ZPU生态系统不同部分背后的设计选择:ISA,数据流,内存和处理元件(PE)内部结构。最后,我们将 ZK 和全同态加密 (FHE) 与最先进的 ASIC 架构进行比较。

介绍

数据驱动的应用程序的快速增长和对隐私的日益增长的需求导致了对保护敏感信息的加密协议的兴趣激增。在这些协议中,零知识证明(ZKP)作为确保计算完整性和隐私性的强大工具脱颖而出。ZKP使一方能够在不泄露任何额外信息的情况下向另一方证明声明的有效性。这一特性导致ZKP在各种以隐私为重点的应用中得到广泛采用,包括区块链技术、安全云计算解决方案和可验证的外包服务。

然而,在实际应用程序中采用ZKP面临着一个重大挑战:与证明生成相关的性能开销。ZKP算法通常涉及对非常大的整数的复杂数学运算,例如椭圆曲线上的大型多项式计算和多标量乘法。此外,密码算法在不断发展,新的和更有效的方案正在快速发展。因此,现有的硬件加速器很难跟上各种各样的加密原语和不断变化的加密算法。

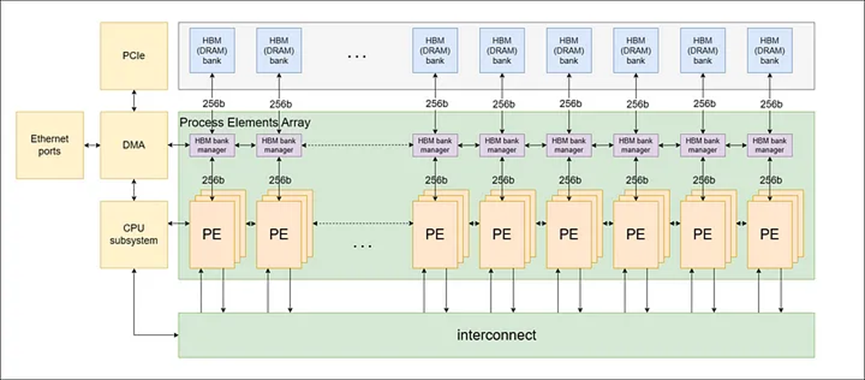

在这篇博客中,我们提出了零知识处理单元(ZPU),这是一种新颖的多功能硬件加速器,旨在解决零知识处理的新需求。ZPU建立在指令集架构(ISA)上,支持可编程性,使其能够适应快速发展的加密算法。ZPU 具有处理元件 (PE) 的互连网络,具有对大字模块化算法的本地支持。PE的核心结构受到乘法累加(MAC)引擎的启发,该引擎是数字信号处理(DSP)和其他计算系统中的基本处理元素。PE的运算符使用模块化算法,其核心组件专门用于支持ZK算法中的常见运算,例如NTT蝴蝶运算和用于多标量乘法的椭圆曲线点加法。

指令集架构

ZPU架构的特点是一个由指令集架构(ISA)定义的处理元件(PE)的互连网络,如下图1所示。我们选择这种架构是为了适应零知识协议不断变化的环境。

ISA 方法使 ZPU 能够保持灵活性,适应ZK算法的变化,并支持广泛的加密原语。此外,使用ISA而不是固定的硬件可以在制造后持续改进软件,确保即使在该领域出现新的进展,ZPU也能保持相关性和效率。

ISA是处理器可以执行的一组指令。它作为硬件和软件之间的接口,定义了软件与硬件交互的方式。通过定制ISA来设计ZPU,我们可以针对ZK处理任务的特定要求对其进行优化,例如大字模算术运算、椭圆曲线加密和其他复杂的密码运算。

- 星际资讯

免责声明:投资有风险,入市须谨慎。本资讯不作为投资建议。